# SYN20708 Datasheet

Dual-Radio Bluetooth 5.4 and IEEE 802.15.4

## 1.1. Description

The Synaptics SYN20708 is a multiprotocol, dual-radio Bluetooth 5.4 system on a chip (SoC) that supports the Bluetooth Classic, Bluetooth Low Energy, Zigbee, Thread, and Matter protocols. The SYN20708 has two BT/BLE/IEEE 802.15.4 cores that can simultaneously function as either a receiver or transmitter. It supports concurrent BT/BLE and IEEE 802.15.4 (Thread and Zigbee) operation on both cores. The SYN20708 also integrates an Arm Cortex-M4 CPU running at 160 MHz and has a high-speed UART interface for connection with an external host processor.

### 1.2. Features

#### 1.2.1. Key Features

- Complies with BT Core Specification Version 5.4 with support for future 6.0 specifications such as high accuracy distance measurement (HADM).

- Supports two 2.4 GHz band radios concurrently.

- Supports Bluetooth Class 1 and Class 2 TX operation.

- Supports Electronic Shelf Label (ESL).

- Supports HADM/channel sounding (BT 6.0 compliance expected).

- Supports BLE-LR, angle of departure (AoD), angle of arrival (AoA), and HW-capable ISOC.

#### 1.2.2. Interfaces

- High-speed UART.

- Synaptics-proprietary Serial Enhanced Coexistence Interface (SECI) for Wi-Fi and BT coexistence.

- 3-wire IEEE 802.15.2 coexistence interface for Wi-Fi and BT coexistence.

- Optional Serial Peripheral Interface (SPI) for direct connection with local external flash.

- I<sup>2</sup>C master to control external sensors.

- Debug UART.

#### 1.2.3. General Features

- Fabricated using a 16 nm FinFET Compact (16FFC) process.

- Supports BLE Zephyr open-source software stack.

- Supports IEEE 802.15.4 (OpenThread and ZBOSS) up to version 2.

- Contains integrated 2.4 GHz power amplifiers and low-noise amplifiers.

- Supports external 2.4 GHz power amplifiers.

- Contains integrated Transmit/Receive (TR) switch.

- Supports external TR switch.

- Supports firmware download over UART for shared flash with a host processor, or from local, dedicated serial flash over an SPI.

- Four GPIO and antenna-selection pins for AoD and AoA determination or HADM (channel sounding).

- Supports secure boot.

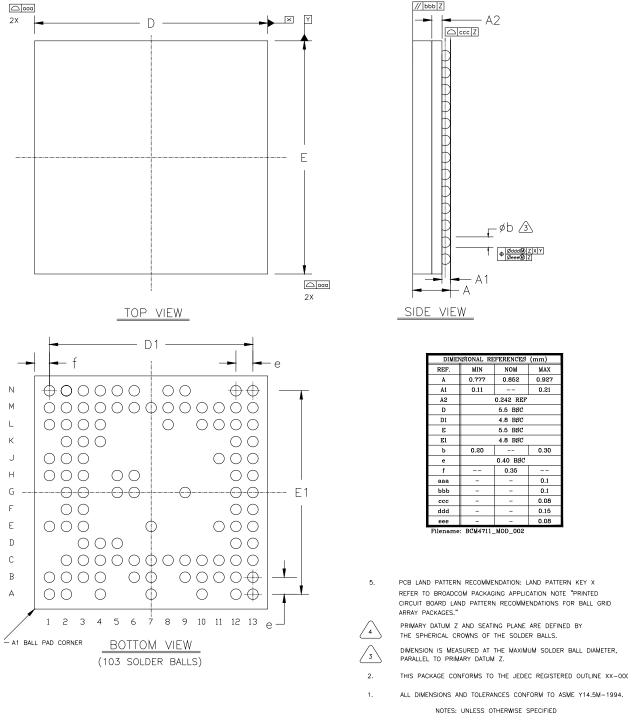

- Package: 103-pin FCBGA, 5.5 mm × 5.5 mm, 0.4 mm pitch.

# Contents

|    | 1.1.<br>1.2.                                                               |                                                                                                | otion es Key Features Interfaces General Features                                                                            | 1<br>1<br>1                                   |

|----|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 1. | Introdu<br>1.1.<br>1.2.                                                    | System                                                                                         | n Overview oth and IEEE 802.15.4 System Overview Standards Support Interfaces Processor and Memory                           | 5.5.6                                         |

| 2. | DC Cha<br>2.1.<br>2.2.<br>2.3.<br>2.4.                                     | Absolut<br>Environ<br>Recomi                                                                   | stics te Maximum Ratings nmental Ratings mended Operating Conditions and DC Characteristics estatic Discharge Specifications | . 7<br>. 7<br>. 8                             |

| 3. | Power 3 3.1. 3.2. 3.3. 3.4.                                                | Power S<br>Power S<br>Power a                                                                  | s and Power Management Supply Topology Sequence and Reset Control Management Unit Electrical Specification                   | 10<br>. 11<br>. 11                            |

| 4. | Freque<br>4.1.                                                             |                                                                                                | erences                                                                                                                      |                                               |

| 5. | <ul><li>5.1.</li><li>5.2.</li><li>5.3.</li><li>5.4.</li><li>5.5.</li></ul> | UART H<br>Periphe<br>Serial F<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>I <sup>2</sup> C Inte<br>Antenn | Serial Enhanced Coexistence Interface                                                                                        | .15<br>.17<br>.18<br>.18<br>.19<br>.20<br>.21 |

| 6. | Bluetoc<br>6.1.<br>6.2.<br>6.3.<br>6.4.<br>6.5.                            | Introdu<br>Bluetod<br>Bluetod<br>Bluetod                                                       | IEEE 802.15.4 RF Specifications Juction                                                                                      | 24<br>24<br>29<br>34                          |

| 7. | Power                                                                      | Consum                                                                                         | nption                                                                                                                       | 36                                            |

| 8. | Packag<br>8.1.<br>8.2.<br>8.3.<br>8.4.<br>8.5.<br>8.6.<br>8.7.             | Pin Mar<br>Signal I<br>GPIO Si<br>GPIO A<br>I/O Stat<br>Packag                                 | nation p Descriptions ignals and Strapping Options Ilternative Signal Functions tes ge Drawing ge Thermal Characteristics    | 37<br>.41<br>42<br>45                         |

www.synaptics.com | Copyright © 2023-2024 Synaptics Incorporated. All Rights Reserved | 505-001427-01 REV 3

| 9.  | Ordering Information | .49 |

|-----|----------------------|-----|

| 10. | Revision History     | .50 |

## 1.Introduction

## 1.1.System Overview

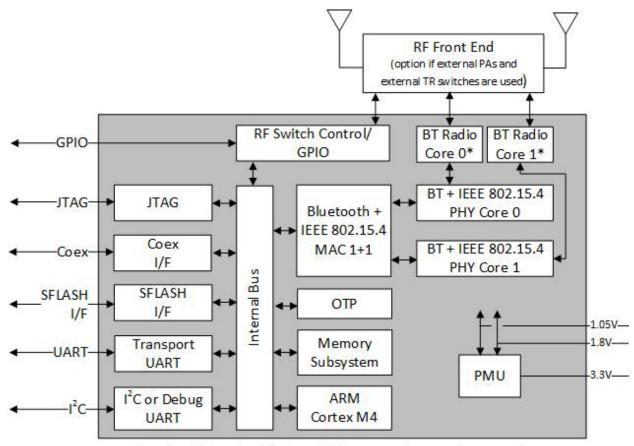

Figure 1 shows a SYN20708 functional block diagram.

\* Each of the radio blocks includes internal PAs and TR switches.

Figure 1. SYN20708 functional block diagram

## 1.2.Bluetooth and IEEE 802.15.4 System Overview

The BT system is a dual-radio Bluetooth 5.4+ compliant baseband processor and 2.4 GHz transceiver. It also has tightly-coupled support for IEEE 802.15.4 (Thread, Zigbee, etc.) using the 2.4 GHz Bluetooth radio.

### 1.2.1.Standards Support

The BT system supports all mandatory SIG BT 5.4+ features. In addition, it supports ranging technologies such as high-accuracy distance measurement (HADM), which is expected to be included in Bluetooth standards greater than BT 5.4+. The SYN20708 also supports worldwide

regulatory requirements and the latest publicly-available revisions of the Thread, Zigbee, and Matter standards.

### 1.2.2.Interfaces

The Bluetooth system supports a standard Host Controller Interface (HCI) via a high-speed UART. It also supports a coexistence interface.

### 1.2.3. Processor and Memory

The BT system includes an Arm core (running at 160 MHz) paired with 1640 KB of ROM memory for program storage and boot ROM, 544 KB of system-data RAM, and 1664 KB of code RAM. It also has 256 bytes of user-accessible OTP for storing wafer ID, RF/analog calibration settings, and other system configuration settings.

# 2.DC Characteristics

**Note:** Values in this data sheet are design goals and are subject to change based on the results of device characterization.

## 2.1. Absolute Maximum Ratings

Caution:

The absolute maximum ratings in Table 1 indicate levels where permanent damage to the device can occur, even if these limits are exceeded for only a brief duration. Functional operation is not guaranteed under these conditions. Operation at absolute maximum conditions for extended periods can adversely affect long-term reliability of the device.

Table 1. Absolute maximum ratings

| Rating                                          | Symbol                                  | Value          | Unit |

|-------------------------------------------------|-----------------------------------------|----------------|------|

| DC supply voltage for digital logic             | VDDC                                    | -0.5 to 0.828  | V    |

| DC supply voltage for baseband PLLs             | BT_VDD_MISCLDO,<br>VDDOUT_MISCLDO       | -0.5 to 0.9844 | V    |

| DC supply voltage for RF analog                 | BT_LDO_VDD1P05,<br>XTAL_VDD1P05         | -0.5 to 1.2075 | V    |

| DC supply voltage for MISCLDO                   | LDO_VDD1P05                             | -0.5 to 1.2075 | V    |

| DC supply voltage for analog I/O                | BT_VDD1P8,<br>OTP_VDD1P8,<br>PMU_VDD1P8 | -0.5 to 2.07   | V    |

| DC supply voltage for Bluetooth PA              | BT_VDD3P3_COREO,<br>BT_VDD3P3_CORE1     | -0.5 to 3.795  | V    |

| DC supply voltage for digital I/O               | PMU_VDDIO,<br>VDDIO (VDDO pin)          | -0.5 to 3.795  | V    |

| External TSSI input                             | TSSI                                    | -0.5 to 1.5    | V    |

| Maximum undershoot voltage for I/O <sup>a</sup> | V <sub>undershoot</sub>                 | -0.5           | V    |

| Maximum overshoot voltage for I/O <sup>a</sup>  | V <sub>overshoot</sub>                  | VDDIO + 0.5    | V    |

| Maximum junction temperature                    | T <sub>j</sub>                          | 110            | °C   |

a. Duration not to exceed 25% of the duty cycle.

# 2.2.Environmental Ratings

The environmental ratings are shown in Table 2.

Table 2. Environmental ratings

| Characteristic                                     | Value                        | Unit | Conditions/Comments               |

|----------------------------------------------------|------------------------------|------|-----------------------------------|

| Ambient Temperature (T <sub>A</sub> ) <sup>a</sup> | -40 to +85 (industrial part) | °C   | Functional operation <sup>b</sup> |

| Storage Temperature                                | -40 to +125                  | °C   | _                                 |

| Relative Humidity                                  | Less than 60                 | %    | Storage                           |

| Relative numbers                                   | Less than 85                 | %    | Operation                         |

- a. See Table 26. Ordering information.

- b. Functionality is guaranteed across this temperature range. Optimal RF performance specified in the data sheet, however, is guaranteed only for –10°C to +55°C without derating performance.

# 2.3. Recommended Operating Conditions and DC Characteristics

**Caution:** Functional operation is not guaranteed outside of the limits shown in Table 3, and operation outside these limits for extended periods can adversely affect long-term reliability of the device.

Table 3. Recommended operating conditions and DC characteristics

| Parameter                           | Symbol                                  | Value           |         |                 |   |

|-------------------------------------|-----------------------------------------|-----------------|---------|-----------------|---|

| raiailletei                         | Symbol                                  | Minimum         | Typical | Maximum         | t |

| DC supply voltage for digital logic | VDDC                                    | 0.6912          | 0.72    | 0.7488          | V |

| DC supply voltage for baseband PLLs | BT_VDD_MISCLDO,<br>VDDOUT_MISCLDO       | 0.8218          | 0.856   | 0.89            | V |

| DC supply voltage for RF analog     | BT_LDO_VDD1P05,<br>XTAL_VDD1P05         | 1.008           | 1.05    | 1.092           | V |

| DC input supply voltage for MISCLDO | LDO_VDD1P05                             | 1.008           | 1.05    | 1.092           | V |

| DC supply voltage for analog I/O    | BT_VDD1P8,<br>OTP_VDD1P8,<br>PMU_VDD1P8 | 1.71            | 1.8     | 1.89            | V |

| DC supply voltage for Bluetooth PA  | BT_VDD3P3_COREO , BT_VDD3P3_CORE1       | 3.135           | 3.3     | 3.465           | V |

| DC supply voltage for digital I/O   | PMU_VDDIO,<br>VDDIO (VDDO pin)          | 3.135           | 3.3     | 3.465           | V |

| External TSSI input                 | TSSI                                    | 0.30            | _       | 1.1             | V |

| Internal POR threshold              | Vth_POR                                 | 0.4             | _       | 0.7             | V |

|                                     | Digital I/O Pin                         | s               |         |                 |   |

| For 3.3V supply:                    |                                         |                 |         |                 |   |

| Input high voltage                  | VIH                                     | 0.65 ×<br>VDDIO | _       | _               | V |

| Input low voltage                   | VIL                                     | _               | _       | 0.35 ×<br>VDDIO | V |

| Output high voltage @ 2 mA          | VOH                                     | VDDIO<br>- 0.40 | _       | _               | V |

| Output low voltage @ 2<br>mA        | VOL                                     | _               | _       | 0.40            | V |

# 2.4. Electrostatic Discharge Specifications

Extreme caution must be exercised to prevent electrostatic discharge (ESD) damage. Proper use of wrist and heel grounding straps to discharge static electricity is required when handling these devices. Always store unused material in its antistatic packaging.

Table 4. ESD specifications<sup>a</sup>

| Condition                                    | ESD Rating                                                  |

|----------------------------------------------|-------------------------------------------------------------|

| Human body model (HBM) contact discharge     | ≥ 1.5 kV (margin capability)<br>1.0 kV (minimum capability) |

| Charged device model (CDM) contact discharge | ≥ 350V (margin capability)<br>250V (minimum capability)     |

a. ESD specifications only apply to production parts. Applicable test specifications: ANSI/ESDA S20.20 2014 JS-001-2014 and ANSI/ESDA S20.20 2014 JS-002-2014.

# 3. Power Supplies and Power Management

## 3.1. Power Supply Topology

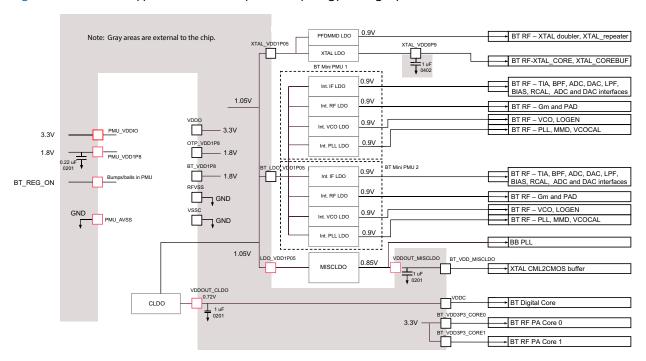

The SYN2O708 contains a power management unit (PMU) and several LDO regulators. All regulators are programmable via the PMU. The PMU is powered by external 3.3V, 1.8V, and 1.05V supplies. All other voltages are provided by internal SYN2O708 LDO regulators.

Figure 2 shows the typical SYN20708 power topology. The gray areas are external to the SYN20708.

Figure 2. Typical power topology

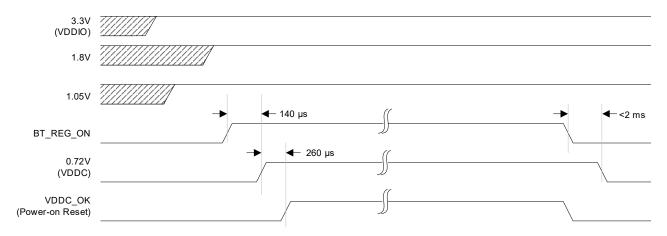

### 3.2. Power Sequence

The SYN20708 provides a low-power shutdown feature that allows the device to be turned off while the host, and any other devices in the system, remain operational. When the SYN20708 is not needed in the system, VDDC is shut down via BT\_REG\_ON while VDDIO remains powered. This allows the SYN20708 to be effectively off while keeping the I/O pins powered so that they do not draw extra current from any other devices connected to the I/O.

During a low-power shutdown state, provided VDDIO remains applied to the SYN20708, all outputs are tristated, and most input signals are disabled. Input voltages must remain within the limits defined for normal operation. This is done to prevent current paths or create loading on any digital signals in the system.

When the SYN20708 is powered on from this state, it is the same as a normal power-up and the device does not retain any information about its state from before it was powered down.

Figure 3 shows the power sequence diagram.

Figure 3. Power sequence diagram

#### 3.3. Power and Reset Control

Table 5 provides the BT\_REG\_ON electrical specification.

| Table 5. BT | REG $O$ | N electrical | specification |

|-------------|---------|--------------|---------------|

|-------------|---------|--------------|---------------|

| Parameter            | Symbol               | Conditions                  | Min. | Typic<br>al | Max.  | Unit |

|----------------------|----------------------|-----------------------------|------|-------------|-------|------|

| Input high voltage   | V <sub>IH</sub>      | For BT_REG_ON               | 1.08 | _           | 3.465 | V    |

| Input low voltage    | V <sub>IL</sub>      | _                           | VSS  | _           | 0.3   | ٧    |

| Pull-down resistance | R <sub>PD</sub>      | _                           | _    | 100         | _     | kΩ   |

| REG OFF time         | T <sub>REG_OFF</sub> | C <sub>REG_ON</sub> ≤ 10 pF | _    | _           | 2     | ms   |

# 3.4. Power Management Unit Electrical Specification

Table 6 provides the PMU electrical specification.

Table 6. PMU electrical specification

| Parameter                                       | Pin Name        | Conditions                                                     | Min.  | Typical | Max.  | Unit |

|-------------------------------------------------|-----------------|----------------------------------------------------------------|-------|---------|-------|------|

| I/O supply voltage 1                            | PMU_VDD1P8      | _                                                              | 1.71  | 1.80    | 1.89  | V    |

| I/O supply voltage 2                            | PMU_VDDIO       | _                                                              | 3.135 | 3.3     | 3.465 | V    |

| I/O supply voltage 3                            | LDO_VDD1P05     | _                                                              | 1.008 | 1.05    | 1.092 | V    |

| Power-up time                                   | T <sub>PU</sub> | CLDO output<br>reaching 0.72V with<br>respect to BT_<br>REG_ON | _     | 171     | _     | μs   |

| PMU_VDD1P8 and<br>PMU_VDDIO power-<br>down time | _               | From 3.3V to 0.3V                                              | _     | _       | 10    | ms   |

Table 7 provides the electrical specification of the internal regulators.

Table 7. Internal regulators electrical specification

| Regulator | Input Supply Voltage (V) |         |         | Output Current (mA) |         |         | Nominal<br>Output |  |

|-----------|--------------------------|---------|---------|---------------------|---------|---------|-------------------|--|

| Regulator | Minimum                  | Typical | Maximum | Minimum             | Typical | Maximum | Voltage (V)       |  |

| CLDO      | 0.9312                   | 1.02    | 1.15    | 0.1                 | _       | 60      | 0.72              |  |

| MISCLDO   | 0.9312                   | 1.02    | 1.15    | 0.1                 | _       | 60      | 0.856             |  |

# 4. Frequency References

An external crystal is used for generating all radio frequencies and normal-operation clocking.

### 4.1. Crystal Interface and Clock Generation

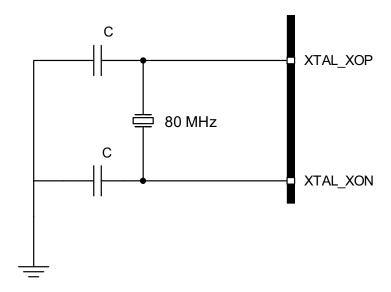

The SYN20708 uses an external crystal to provide a frequency reference. The recommended configuration for the crystal oscillator including all external components is shown in Figure 4. Consult the reference schematics for the latest configuration.

Figure 4. Recommended oscillator configuration

The recommended default frequency reference is an 80 MHz crystal. The signal characteristics for the crystal oscillator interface are provided in Table 8.

**Note:** Although the synthesizer can support alternative reference frequencies, frequencies other than the default require support to be added in the driver, plus additional extensive system testing. Contact Synaptics for further details.

| Table 8. Cr | vstal | oscillator | requirem    | ontsª  |

|-------------|-------|------------|-------------|--------|

| Table U. Ci | ystai | USCIIIALUI | ı cyun ciin | - וונט |

| Parameter                                                                                           | Conditions/Notes        |      |         |      |      |

|-----------------------------------------------------------------------------------------------------|-------------------------|------|---------|------|------|

| T didiliotoi                                                                                        | Gorial tions, it of the | Min. | Typical | Max. | Unit |

| Frequency                                                                                           | _                       | _    | 80      | _    | MHz  |

| Frequency tolerance over<br>the lifetime of the<br>equipment, including<br>temperature <sup>c</sup> | Without trimming        | -20  | _       | 20   | ppm  |

| Crystal load capacitance                                                                            | _                       | _    | 8       | _    | pF   |

| ESR                                                                                                 | _                       | _    | _       | 50   | Ω    |

Table 8. Crystal oscillator requirements<sup>a</sup> (continued)

| Parameter    | Conditions/Notes                                            |      |         |      |      |

|--------------|-------------------------------------------------------------|------|---------|------|------|

| i didilictei |                                                             | Min. | Typical | Max. | Unit |

| Drive level  | External crystal must be able to tolerate this drive level. | 150  | _       | _    | μW   |

- a. The parameter values in this table apply when using an 80 MHz crystal.

- b. Use XTAL\_XOP and XTAL\_XON.

- c. It is the responsibility of the equipment designer to select oscillator components that comply with these specifications.

# 5.Bluetooth System Interfaces

### 5.1.UART Host Interface

The SYN20708 UART host interface is a standard 4-wire interface (RX, TX, RTS, and CTS) with adjustable baud rates from 9600 bps to 12 Mbps. The baud rate may be selected through a vendor-specific UART HCI command.

The UART has a 2600-byte receive FIFO and a 2600-byte transmit FIFO to support host-transport traffic. Access to the FIFOs is conducted through the AHB interface through either DMA or the CPU. The UART supports the Bluetooth 5.4 UART HCI specification: H4, a custom Extended H4, and H5, as well as the OpenThread Spinel protocol. The default baud rate is 115.2 Kbaud.

The UART supports the 3-wire H5 UART transport, as described in the Bluetooth specification (*Three-wire UART Transport Layer*). Compared to H4, the H5 UART transport reduces the number of signal lines required by eliminating the CTS and RTS signals.

The SYN2O708 UART can perform XON/XOFF flow control and includes hardware support for the Serial Line Input Protocol (SLIP). It can also perform wake-on activity. For example, activity on the RX or CTS inputs can wake the chip from a sleep state.

Normally, the UART baud rate is set by a configuration record downloaded after device reset. Support for changing the baud rate during normal HCI UART operation is included through a vendor–specific command that allows the host to adjust the contents of the baud rate registers. The SYN20708 UARTs operate correctly with the host UART as long as the combined baud rate error of the two devices is within ±2%.

Table 9. Example of common Baud rates

| Desired Rate | Actual Rate | Error (%) |

|--------------|-------------|-----------|

| 12000000     | 12000000    | 0.00      |

| 9600000      | 9600000     | 0.00      |

| 8000000      | 8000000     | 0.00      |

| 6000000      | 6000000     | 0.00      |

| 4000000      | 4000000     | 0.00      |

| 3692000      | 3692308     | 0.01      |

| 3000000      | 3000000     | 0.00      |

| 2000000      | 2000000     | 0.00      |

| 1500000      | 1500000     | 0.00      |

| 1444444      | 1454544     | 0.70      |

| 921600       | 923077      | 0.16      |

| 460800       | 461538      | 0.16      |

| 230400       | 230796      | 0.17      |

| 115200       | 115385      | 0.16      |

| 57600        | 57692       | 0.16      |

| 38400        | 38400       | 0.00      |

| 28800        | 28846       | 0.16      |

| 19200        | 19200       | 0.00      |

| 14400        | 14423       | 0.16      |

| 9600         | 9600        | 0.00      |

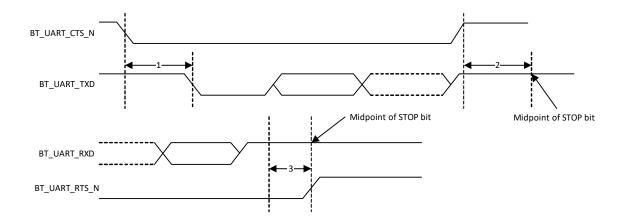

Figure 5. UART timing

Table 10. UART Timing specifications

| Reference | Characteristics                                            | Minimum | Typical | Maximum | Unit        |

|-----------|------------------------------------------------------------|---------|---------|---------|-------------|

| 1         | Delay time, BT_UART_CTS_N low to BT_UART_TXD valid         | _       | _       | 1.5     | Bit periods |

| 2         | Setup time, BT_UART_CTS_N high before midpoint of stop bit | _       | _       | 0.5     | Bit periods |

| 3         | Delay time, midpoint of stop bit to BT_UART_RTS_N high     | _       | _       | 0.5     | Bit periods |

### 5.2.Peripheral/Debug UART Interface

The peripheral/debug UART has the following features:

- 256-byte RX and TX FIFOs.

- A 4-pin interface.

The PUART\_RXD and PUART\_TXD signals can be multiplexed to one of the following three pairs of pins, respectively:

- ETRSW\_CTRLO and ETRSW\_CTRL1

- ANT\_SEL2 and ANT\_SEL1

- TX\_CONFX2 and BT\_STATUS2

Table 11 shows the rates supported by the peripheral/debug UART.

Table 11. Peripheral/Debug UART supported rates

| Desired Rate | Actual Rate | Error (%) |

|--------------|-------------|-----------|

| 3000000      | 3000000     | 0.00      |

| 2000000      | 2000000     | 0.00      |

| 1500000      | 1500000     | 0.00      |

| 1444444      | 1454544     | 0.70      |

| 921600       | 923077      | 0.16      |

| 460800       | 461538      | 0.16      |

| 230400       | 230796      | 0.17      |

| 115200       | 115385      | 0.16      |

| 57600        | 57692       | 0.16      |

| 38400        | 38400       | 0.00      |

| 28800        | 28846       | 0.16      |

| 19200        | 19200       | 0.00      |

| 14400        | 14423       | 0.16      |

| 9600         | 9600        | 0.00      |

#### 5.3. Serial Flash Interface

The serial flash interface supports the following features:

- A SPI-compatible serial bus.

- A maximum serial flash size of 64 MB.

- A 24 MHz (maximum) clock frequency.

- Support for either ×1 or ×4 addresses with two data lines (one input and one output).

- 3-byte and 4-byte addressing modes.

- A configurable dummy-cycle count that is programmable from 1 to 15.

- Programmable instructions output to serial flash.

- An option to change the sampling edge from rising-edge to falling-edge for read-back data when in highspeed mode.

**Note:** To minimize ripple at the SYN20708 SPI\_CLK port to within ±20% of VDDIO due to transmission-line effects, use a series resistor on the SPI\_CLK line to the serial flash, preferably close to the serial flash port.

### 5.3.1. Serial Flash Timing

#### 5.3.1.1.Read-Register Timing

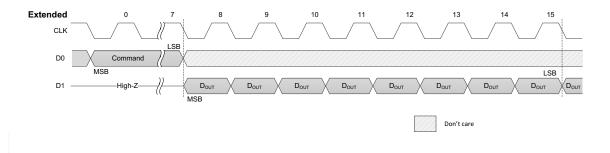

Figure 6 shows the serial flash extended read-register timing.

**Note:** Regarding Figure 6, all Read Register commands except Read Lock Register are supported. A Read Nonvolatile Configuration Register operation will output data starting from the least significant byte.

Figure 6. Serial flash read-register timing

#### 5.3.1.2. Write-Register Timing

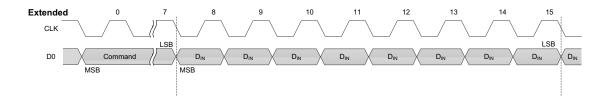

Figure 7 shows the serial flash extended write-register timing.

**Note:** Regarding Figure 7:

- All write-register commands except Write Lock Register are supported.

- The waveform must be extended for each protocol to 23.

- A Write Nonvolatile Configuration Register operation requires data to be sent starting from the least significant byte.

Figure 7. Serial flash write-register timing

### 5.3.1.3. Memory Fast-Read Timing

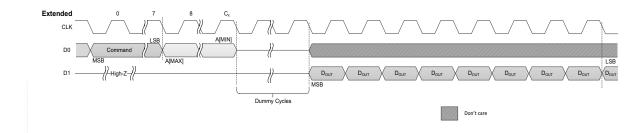

Figure 8 shows the serial flash extended memory fast-read timing.

Note: Regarding Figure 8:

- 24-bit addressing is used, so A[MAX] = A[23] and A[MIN] = A[0].

- For an extended SPI protocol,  $C_X = 7 + (A[MAX] + 1)$ .

Figure 8. Memory fast-read timing

### 5.3.1.4. Memory-Write Timing

Figure 9 shows the serial flash extended memory-write (Page Program) timing.

**Note:** Regarding Figure 9, for an extended SPI protocol,  $C_X = 7 + (A[MAX] + 1)$ .

Figure 9. Memory-write timing

#### 5.3.2. Serial Flash Parameters

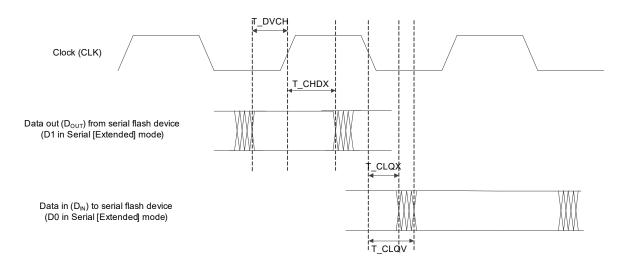

The combination of Figure 10 and Table 12 provides the serial flash timing parameters.

Figure 10. Serial flash timing parameters diagram

Table 12. Serial flash timing parameters

| Parameter | Description                           | Minimum | Maximum | Unit |

|-----------|---------------------------------------|---------|---------|------|

| T_DVCH    | Data setup time                       | 2       | _       | ns   |

| T_CHDX    | Data hold time                        | 3       | _       | ns   |

| T_CLQX    | Output hold time                      | 1       | _       | ns   |

| T_CLQV    | Output valid time (with a 10 pF load) | _       | 5       | ns   |

#### 5.3.3. Serial Enhanced Coexistence Interface

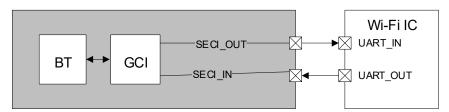

An external handshake interface is available to enable signaling between the device and an external co-located wireless device, such as a Wi-Fi IC, to manage wireless medium sharing for optimum performance.

Figure 11 shows the Wi-Fi coexistence interface. See Table 10, "UART Timing specifications," on page 17 for UART baud rate.

NOTE: SECI\_OUT and SECI\_IN are multiplexed on the GPIOs.

Figure 11. Serial enhanced coexistence interface

# 5.4.I<sup>2</sup>C Interface

The SYN20708 supports a  $I^2C$  master interface. The Standard, Fast, and Fast-mode Plus modes are supported.

The  $I^2C$  interface is a 2-wire serial bus that is compatible with the  $I^2C$  Specification (version 2.1). The SYN20708  $I^2C$  interface supports the following features:

- Parallel-to-I<sup>2</sup>C bus protocol converter and interface.

- Standard mode (100 kbps), Fast mode (400 kbps), and Fast-mode Plus (1 Mbps).

- Single-master capability.

- Support for both 7-bit and 10-bit addressing.

- Available as a GPIO alternate function.

- · Clock and data glitch filtering.

The SCL and SDA signals can be multiplexed to one of the following four pairs of pins, respectively:

- TDO and TDI.

- EPA\_CTRL1 and EPA\_CTRL0.

- ANT\_SEL1 and ANT\_SEL2.

- SPI\_MISO and SPI\_MOSI.

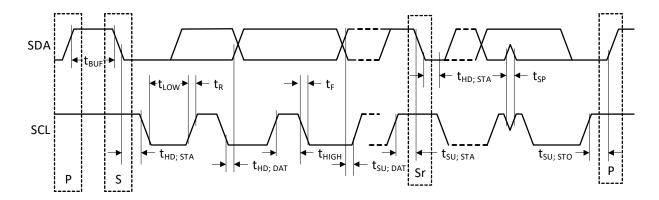

The I<sup>2</sup>C interface timing specifications are defined in Table 13 and Figure 12.

Table 13. PC timing specifications

|                                                                                              |                     | Fast             | Uni         |                  |     |  |

|----------------------------------------------------------------------------------------------|---------------------|------------------|-------------|------------------|-----|--|

| Parameter                                                                                    | Symbol              | Minimu<br>m      | Typica<br>I | Maximu<br>m      | t   |  |

| SCL clock frequency                                                                          | f <sub>SCL</sub>    | 0                | _           | 1000             | kHz |  |

| Bus-free times between a stop and start condition                                            | t <sub>Buf</sub>    | 500              | -           | _                | ns  |  |

| Hold time (repeated) start condition. After this period, the first clock pulse is generated. | t <sub>HD;STA</sub> | 260              | _           | _                | ns  |  |

| Low period of the SCL clock                                                                  | t <sub>LOW</sub>    | 500              | _           | _                | ns  |  |

| High period of the SCL clock                                                                 | t <sub>HIGH</sub>   | 260              | _           | _                | ns  |  |

| Set-up time for a repeated start condition                                                   | t <sub>SU;STA</sub> | 260              | _           | _                | ns  |  |

| Data hold time                                                                               | t <sub>HD;DAT</sub> | Oc               | _           | 450 <sup>d</sup> | ns  |  |

| Data setup time                                                                              | t <sub>SU;DAT</sub> | 260 <sup>e</sup> | _           | _                | ns  |  |

| Setup time for stop condition                                                                | t <sub>SU;STO</sub> | 260              | _           | _                | ns  |  |

| Pulse width of spikes suppressed by the input filter                                         | t <sub>SP</sub>     | 0                | _           | 10               | ns  |  |

- a. All timing values are referenced to minimum (V<sub>IH</sub>) and maximum (V<sub>IL</sub>) levels and were obtained over process, voltage, and temperature.

- b. For Fast-mode Plus, the hardware currently supports the 4th mode, not the 3rd mode.

- c. A device must internally provide a hold time of at least 300 ns for the serial data (SDA) signal to bridge the undefined region of the serial clock line (SCL).

- d. This must be met because the SYN20708 does not stretch the low period of the SCL signal.

- e. A Fast-mode Plus device can be used in Fast mode or Standard mode, but the T<sub>SU,DAT</sub> > 100 ns (Fast mode) or T<sub>SU;DAT</sub> > 250 ns (Standard mode) requirement must be met. This automatically applies because the SYN20708 does not stretch the low period of the SCL signal for Fast-mode Plus.

Figure 12. Clock and data timing

The SDA and SCL lines can source and sink 2 mA and have internal 45 k $\Omega$  pull-up resistors. To drive the capacitive load of the I<sup>2</sup>C interface, external pull-up resistors will be required to keep the rise time less than 300 ns between 30% of VDD\_IO and 70% of VDD\_IO. The rise time is modeled by a

simple RC circuit where R is the total pull-up resistance (the parallel combination of the internal and external resistors) and C is the total capacitance of the signal line, the trace capacitance, and all connected pins.

$$V(t) = VDD_IO \times (1 - e^{-t/RC})$$

Since the rise time from 30% to 70% of VDD\_IO must be less than 300 ns, the maximum value of R is:

$$R_{\text{max}} < (300 \times 10^{-9})/(0.8473 \times C)$$

The minimum value of R is limited by the 2 mA pull-down capability of the SDA and SCL drivers:

$$R_{min} > (VDD_IO / 2 mA)$$

This gives minimum R values of  $900\Omega$  when VDD\_IO is 1.8V. Taking into consideration the minimum value of the internal 35 k $\Omega$  pull-up (R<sub>int</sub>), the value of the external resistor (R<sub>ext</sub>) is:

$$R_{ext} = (R \times R_{int})/(R_{int} - R)$$

Thus, if the calculated total pull-up value of R is  $900\Omega$ , then the minimum value of  $R_{ext}$  is  $924\Omega$  for a line with very high capacitance. A value of 1.8 k $\Omega$  for  $R_{ext}$  is usually sufficient.

#### 5.5. Antenna Selection Interface

The SYN20708 supports up to four pins (ANT\_SEL0-ANT\_SEL3) that can be used to connect to a 16-antenna array for AoA, AoD, or channel sounding (CS). (CS uses a maximum of four antennas.) These pins are programmed as outputs when they are used to control an external RF switch, and they are designed to support switching speeds as fast as one µs.

Table 14 describes the four pins when they're used as antenna-switching control signals.

Table 14. Antenna switching control pins

| Pin Name | Description                                                |

|----------|------------------------------------------------------------|

| ANT_SELO | Defaults as bit 0 of an AoA, AoD, or CS antenna selection. |

| ANT_SEL1 | Defaults as bit 1 of an AoA, AoD, or CS antenna selection. |

| ANT_SEL2 | Defaults as bit 2 of an AoA or AoD antenna selection.      |

| ANT_SEL3 | Defaults as bit 3 of an AoA or AoD antenna selection.      |

# 6.Bluetooth and IEEE 802.15.4 RF Specifications

### 6.1.Introduction

**Note:** Values in this data sheet are design goals and are subject to change based on device characterization results.

Unless otherwise stated, limit values apply for the conditions specified in Table 2, "Environmental ratings," on page 7 and "Recommended Operating Conditions and DC Characteristics" on page 8.

Typical values apply for an ambient temperature of +25°C.

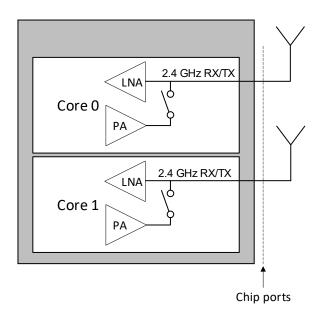

Figure 13 shows the Bluetooth RF port configuration. Separate RX and TX can be accommodated for external PAs and LNAs.

Figure 13. Bluetooth RF port configuration

Note: Unless otherwise specified, all Bluetooth specifications are measured at the chip port.

## 6.2.Bluetooth 2.4 GHz Receiver Performance Specification

**Note:** Table 15 applies to each radio, and unless otherwise defined, all values are measured at the chip RF input port.

Table 15. Bluetooth 2.4 GHz receiver specification (derived from simulation)

| Paramete<br>r      | Conditions |   | Min  | Typical | Max      | Unit |  |

|--------------------|------------|---|------|---------|----------|------|--|

|                    | General    |   |      |         |          |      |  |

| Frequency<br>Range |            | - | 2402 | _       | 248<br>0 | MHz  |  |

Table 15. Bluetooth 2.4 GHz receiver specification (derived from simulation)

| Paramete<br>r                                    | Conditions                                                     |                                | Min              | Typical | Max            | Unit     |     |

|--------------------------------------------------|----------------------------------------------------------------|--------------------------------|------------------|---------|----------------|----------|-----|

| Receive                                          | 1 Mbps, GFSK BDR, 0.1%                                         |                                | 1% BER           | _       | -92.5          | -90      |     |

| sensitivity<br>with dirty                        |                                                                | 2 Mbps, π/4-DQPSK I            | EDR-2, 0.01% BER | _       | -95            | -92      |     |

| transmit off (BDR and EDR modes)                 | Normal-Power<br>mode,<br>no MRC                                | 3 Mbps, 8-DQPSK ED             | R-3, O.01% BER   | _       | -89            | -86      |     |

|                                                  | Normal-Power                                                   | 1 Mbps, GFSK BDR, O.           | 1% BER           | _       | -95            | _        |     |

|                                                  | mode with<br>MRC                                               | 2 Mbps, π/4-DQPSK<br>BER       | EDR-2, 0.01%     | _       | -98            | _        |     |

|                                                  |                                                                | 3 Mbps, 8-DQPSK ED             | R-3, 0.01% BER   | _       | -92            | _        |     |

|                                                  |                                                                |                                | 125 kbps         | _       | - 108.5        | -<br>106 | dBm |

|                                                  | 37-byte payload,<br>standard<br>modulation index,<br>30.8% PER | 500 kbps                       | _                | - 103.5 | -101           | dBm      |     |

|                                                  |                                                                | modulation index,              | 1 Mbps           | _       | - 97.5         | -95      | dBm |

|                                                  |                                                                |                                | 2 Mbps           | _       | - 94.5         | -92      | dBm |

|                                                  | Named Pause                                                    |                                | 125 kbps         | _       | - 108.5        | -<br>106 | dBm |

|                                                  |                                                                | 255-byte payload,<br>standard  | 500 kbps         | _       | - 102.5        | -<br>100 | dBm |

|                                                  | Normal-Power mode,                                             | modulation index,<br>30.2% PER | 1 Mbps           | _       | - 96.5         | -94      | dBm |

|                                                  | no MRC                                                         |                                | 2 Mbps           | _       | - 93.5         | -91      | dBm |

|                                                  |                                                                |                                | 125 kbps         | _       | <b>– 111.5</b> | _        | dBm |

|                                                  |                                                                | 37-byte payload,               | 500 kbps         | _       | - 106.5        | _        | dBm |

|                                                  |                                                                | standard<br>modulation index,  | 1 Mbps           | _       | - 100.5        | _        | dBm |

|                                                  |                                                                | 30.8% PER                      | 2 Mbps           | _       | - 97.5         | _        | dBm |

| Receive<br>sensitivity<br>with dirty<br>transmit |                                                                |                                | 125 kbps         | _       | <b>– 111.5</b> | _        | dBm |

|                                                  |                                                                | 255-byte payload,              | 500 kbps         | _       | - 105.5        | _        | dBm |

| off<br>(BLE                                      | Normal-Power                                                   | standard<br>modulation index,  | 1 Mbps           | _       | - 99.5         | _        | dBm |

| modes)                                           | des) mode with 30                                              | 30.2% PER                      | 2 Mbps           | _       | - 96.5         | _        | dBm |

Table 15. Bluetooth 2.4 GHz receiver specification (derived from simulation)

| Paramete<br>r                                            | Conditions                                                        | Min | Typical | Max | Unit        |

|----------------------------------------------------------|-------------------------------------------------------------------|-----|---------|-----|-------------|

| Receive<br>sensitivity<br>degradatio<br>n on<br>spurious | BDR, EDR-2, EDR-3<br>BLE (125 kbps, 500 kbps, 1 Mbps, and 2 Mbps) |     | _       | 2   | dB          |

| Input in-                                                | Maximum LNA gain                                                  | -12 | _       | _   | dBm         |

| band IIP3                                                | Minimum LNA gain                                                  | 0   | _       | _   | dBm         |

| Maximum receive                                          | BDR, EDR-2, EDR-3                                                 | -17 | _       | _   |             |

|                                                          | BLE (125 kbps, 500 kbps, 1 Mbps, and 2 Mbps)                      | -10 | _       | _   | dBm         |

| No<br>damage<br>max.                                     | BDR, EDR-2, EDR-3, BLE modes                                      | 13  | _       | _   | dBm         |

| RX LO<br>leakage                                         | BDR, EDR-2, EDR-3, BLE modes                                      | _   | _       | -50 | dBm/<br>MHz |

| RSSI<br>accuracy                                         | Connected modes                                                   | -2  | _       | 2   | dBm         |

| with calibration @ system level.                         | BLE scan mode (when listening to BLE advertisement channels)      | -2  | _       | 2   | dBm         |

| See section 12.4.3 of the requireme nts                  | BLE connected mode                                                | -2  | _       | 2   | dBm         |

| General<br>spurs (LO,<br>AFE, VCO,<br>XTAL+LO),          | _                                                                 | _   | _       | -50 | dBm/<br>MHz |

| Return loss                                              | $Z_0 = 50\Omega$ across the RX dynamic range                      | _   | 10      | _   | dB          |

|                                                          | Interference Performance <sup>a</sup>                             |     |         |     |             |

| C/I co-                                                  | GFSK, 0.1% BER                                                    | _   | _       | 11  | dB          |

| C/I 1 MHz<br>adjacent<br>channel                         | GFSK, 0.1% BER                                                    | _   | _       | 0   | dB          |

| C/I 2 MHz<br>adjacent<br>channel                         | GFSK, 0.1% BER                                                    | _   | _       | -30 | dB          |

| C/I≥3 MHz<br>adjacent<br>channel                         | GFSK, 0.1% BER                                                    | _   | _       | -40 | dB          |

| C/I image<br>channel                                     | GFSK, 0.1% BER                                                    | _   | _       | -9  | dB          |

www.synaptics.com | Copyright © 2023-2024 Synaptics Incorporated. All Rights Reserved | 505-001427-01 REV 3

Table 15. Bluetooth 2.4 GHz receiver specification (derived from simulation)

| Paramete<br>r                     | Conditions                                                            |       | Typical | Max | Unit |  |  |

|-----------------------------------|-----------------------------------------------------------------------|-------|---------|-----|------|--|--|

| C/I 1 MHz<br>adjacent<br>to image | GFSK, 0.1% BER                                                        | _     | _       | -20 | dB   |  |  |

| C/I co-                           | $\pi/4$ -DQPSK, 0.1% BER                                              | _     | _       | 13  | dB   |  |  |

| C/I 1 MHz                         | $\pi/4$ -DQPSK, 0.1% BER                                              | _     | _       | 0   | dB   |  |  |

| C/I 2 MHz                         | $\pi/4$ -DQPSK, 0.1% BER                                              | _     | _       | -30 | dB   |  |  |

| C/I≥3MHz                          | $\pi/4$ -DQPSK, 0.1% BER                                              | _     | _       | -40 | dB   |  |  |

| C/I image                         | $\pi/4$ -DQPSK, 0.1% BER                                              | _     | _       | -7  | dB   |  |  |

| C/I 1 MHz                         | $\pi/4$ -DQPSK, 0.1% BER                                              | _     | _       | -20 | dB   |  |  |

| C/I co-                           | 8-DPSK, 0.1% BER                                                      | _     | _       | 21  | dB   |  |  |

| C/I 1 MHz                         | 8-DPSK, 0.1% BER                                                      | _     | _       | 5   | dB   |  |  |

| C/I 2 MHz                         | 8-DPSK, 0.1% BER                                                      | _     | _       | -25 | dB   |  |  |

| C/I≥3 MHz                         | 8-DPSK, 0.1% BER                                                      | _     | _       | -33 | dB   |  |  |

| C/I image                         | 8-DPSK, 0.1% BER                                                      | _     | _       | 0   | dB   |  |  |

| C/I 1 MHz                         | 8-DPSK, 0.1% BER                                                      | _     | _       | -13 | dB   |  |  |

|                                   | Out-of-Band Blocking Performance                                      | e(CW) |         |     |      |  |  |

|                                   | 30-2000 MHz                                                           | _     | -10     | _   | dBm  |  |  |

| Normal-<br>Power                  | 2000-2399 MHz 0.1% BER                                                | _     | -27     | _   | dBm  |  |  |

| mode                              | 2498-3000 MHz 0.1% BER                                                | _     | -27     | _   | dBm  |  |  |

|                                   | 3000 MHz–12.75<br>GHz 0.1% BER                                        | _     | -27     | _   | dBm  |  |  |

|                                   | Out-of-Band Blocking Performance, Modulated Interferer <sup>b c</sup> |       |         |     |      |  |  |

Table 15. Bluetooth 2.4 GHz receiver specification (derived from simulation)

| Paramete<br>r                   | Conditions         |                                | Min | Typical          | Max | Unit |

|---------------------------------|--------------------|--------------------------------|-----|------------------|-----|------|

|                                 | 600-960 MHz        | LB1 with LTE and WCDMA signal  | -25 | -15              | _   | dBm  |

|                                 | 1700-2025<br>MHz   | MB with LTE and WCDMA signal   | -25 | -15              | _   | dBm  |

|                                 | 824-849 MHz        | GSM850 with GSM signal         | -23 | -15              | _   | dBm  |

|                                 | 880-915 MHz        | E-GSM with GSM signal          | -23 | -15              | _   | dBm  |

|                                 | 1710-1785 MHz      | GSM1800 with GSM signal        | -25 | -15              | _   | dBm  |

|                                 | 1850-1910<br>MHz   | GSM1800 with GSM signal        | -25 | -25              | _   | dBm  |

| Normal-<br>Power                | 2300-2370<br>MHz   | B40A with LTE signal           | _   | -25              | _   | dBm  |

| mode                            | 2330-2370<br>MHz   | B40B with LTE signal           | _   | TBD <sup>d</sup> | _   | dBm  |

| Applies to<br>GFSK (1<br>Mbps), | 2370-2400<br>MHz   | B40B with LTE signal           | _   | -35              | _   | dBm  |

| π/4-DPSK                        | 2400-2483.5<br>MHz | ISM with WLAN reference signal | -46 | TBD              | _   | dBm  |

| Mbps),<br>and 8-                | 2496-2510<br>MHz   | B41 with LTE signal            | _   | -25              | _   | dBm  |

| DPSK (3<br>Mbps)                | 2510-2690<br>MHz   | B41 with LTE signal            | _   | -15              | _   | dBm  |

|                                 | 3400-3800<br>MHz   | B42/43 w/LTE signal            | -25 | -15              | _   | dBm  |

|                                 | 3300-4200<br>MHz   | 5G NR n77                      | -25 | -15              | _   | dBm  |

|                                 | 4400-5000<br>MHz   | 5G NR n79                      | -25 | -15              | _   | dBm  |

|                                 | 5150-5925<br>MHz   | WLAN HT20 MCS0 signal          | -30 | -15              | _   | dBm  |

|                                 | 6240-7987<br>MHz   | UWB CH5-CH8 signal             | -30 | -15              | _   | dBm  |

|                                 | 7488-8736<br>MHz   | UWB CH9–CH10 signal            | -30 | -15              | _   | dBm  |

|                                 |                    | Spurious Emissions             |     |                  |     |      |

Table 15. Bluetooth 2.4 GHz receiver specification (derived from simulation)

| Paramete<br>r         | Conditions    | Min | Typical | Max | Unit    |

|-----------------------|---------------|-----|---------|-----|---------|

|                       | 30 MHz-1 GHz  | _   | -90     | ı   | dBm     |

|                       | 1–12.75 GHz   | _   | -90     | ı   | dBm     |

|                       | 851–894 MHz   | _   | -165    | -   | dBm/ Hz |

| Normal-<br>Power mode | 925-960 MHz   | _   | -165    | _   | dBm/ Hz |

|                       | 1805–1880 MHz | _   | -165    | _   | dBm/ Hz |

|                       | 1930–1990 MHz | _   | -165    | _   | dBm/ Hz |

|                       | 2110-2170 MHz | _   | -165    | _   | dBm/ Hz |

# 6.3.Bluetooth 2.4 GHz Transmitter Performance Specification

Table 16 applies to each core, and unless otherwise defined, all values are measured at the chip RF Note: input port.

Table 16. Bluetooth 2.4 GHz transmitter RF specification (derived from simulation)

| Parameter       | Conditions | Min. | Typical | Max. | Unit |  |  |

|-----------------|------------|------|---------|------|------|--|--|

| General         |            |      |         |      |      |  |  |

| Frequency range | _          | 2402 | _       | 2480 | MHz  |  |  |

a. The maximum value represents the actual Bluetooth Low Energy specification required for Bluetooth Low Energy qualification as defined in the version 4.7 specification.

b. For LTE bands, measure 3 dB RX sensitivity degradation with 16-QAM 1 RB, 12 RB, 25 RB, and 100 RB uplink signals. Use 200 RB where applicable. For 2.4 GHz ISM band, measure 3 dB RX sensitivity degradation with a WLAN HT20 MCS0 jammer signal. The WLAN jammer is set for 2437 MHz; the desired Bluetooth signal is offset ±30 MHz (typical), ±15 MHz (minimum).

c.Blocking level for 3 dB RX sensitivity degradation at the chip input for the modulation indicated with a 0.01% BER and without external filtering.

d. Due to a notch filter limitation, this can't be measured accurately.

Table 16. Bluetooth 2.4 GHz transmitter RF specification (derived from simulation) (continued)

| Parameter                                                                                                                                                                         | Cond                                                                                   | litions                                                        | Min.                                           | Typical | Max. | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------|---------|------|------|

|                                                                                                                                                                                   |                                                                                        | BDR, GFSK                                                      | _                                              | 14      | _    | _    |

|                                                                                                                                                                                   |                                                                                        | EDR-2, π/4-<br>DQPSK                                           | _                                              | 11      | _    | _    |

|                                                                                                                                                                                   | Normal-                                                                                | EDR-3, 8-<br>DPSK                                              | _                                              | 11      | _    | _    |

| TX output power  (TX power at chip                                                                                                                                                | Power mode                                                                             | BLE (1 Mbps, 2<br>Mbps,<br>500 kbps, and<br>125 kbps),<br>GFSK | _                                              | 14      | _    | dBm  |

| output that meets  Bluetooth Test                                                                                                                                                 |                                                                                        | BDR, GFSK                                                      | _                                              | 20      | _    | _    |

| Specification RF.TS.4.0.0 ACP/EVM requirements.                                                                                                                                   |                                                                                        | EDR-2, π/4-<br>DQPSK                                           | _                                              | 15      | _    | _    |

| Also, all TX output power requirements shall be met for 2:1 VSWR for all                                                                                                          | Beamforming mode                                                                       | EDR-3, 8-<br>DPSK                                              | _                                              | 15      | _    | _    |

| phase angles over VT.                                                                                                                                                             | mode                                                                                   | BLE (1 Mbps, 2<br>Mbps,<br>500 kbps, and<br>125 kbps),<br>GFSK | _                                              | 20      | _    | dBm  |

|                                                                                                                                                                                   | High-Power Mbps, 500 Mbps, and ePA)  BLE (1Mbps, 2 Mbps, 500 kbps, and 125 kbps), GFSK |                                                                | Dependent on the external PA and board design. |         |      | dBm  |

| Output power variation with 3:1 VSWR (Chip shall meet all ACP/EVM requirements specified in <i>Bluetooth Test Specification RF.TS.4.0.0</i> under 3:1 VSWR for all phase angles.) | _                                                                                      |                                                                | -2                                             | _       | 2    | dB   |

| Power control step                                                                                                                                                                | _                                                                                      |                                                                | 2                                              | 4       | 8    | dB   |

| Power control accuracy over process (Output power will include calibration.)                                                                                                      | BDR, EDR-2, EDF                                                                        | R-3,BLE modes                                                  | -1                                             | _       | 1    | dB   |

| TX power control<br>dynamic range                                                                                                                                                 | Applies to both power and high                                                         |                                                                | _                                              | 30      | _    | dB   |

| Gain control step                                                                                                                                                                 | For setting outp                                                                       | out power                                                      | _                                              | _       | 0.25 | dB   |

| Return loss at chip TX port                                                                                                                                                       | Z <sub>0</sub> = 50Ω, acros<br>dynamic range                                           | $Z_0 = 50\Omega$ , across the TX dynamic range                 |                                                | 8       | _    | dB   |

| BDR GFSK TX output spectrum                                                                                                                                                       | -20 dBc BW (20                                                                         | O dB bandwidth)                                                | _                                              | 0.93    | 1    | _    |

www.synaptics.com | Copyright © 2023-2024 Synaptics Incorporated. All Rights Reserved | 505-001427-01 REV 3

Table 16. Bluetooth 2.4 GHz transmitter RF specification (derived from simulation) (continued)

| Parameter |                                                   | Conditions                                                                                                         | Min. | Typical | Max. | Unit |  |

|-----------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------|---------|------|------|--|

|           | In-Band Spurious Emissions <sup>a</sup>           |                                                                                                                    |      |         |      |      |  |

| EDR       | 1.0 MHz <  M –<br>N  < 1.5 MHz                    | M – N = the frequency range for which the spurious emission is measured relative to the transmit center frequency  | _    | -38     | -26  | _    |  |

|           | 1.5 MHz <  M –<br>N  < 2.5 MHz                    |                                                                                                                    | _    | -30     | -20  | _    |  |

|           | M – N  ≥ 2.5<br>MHz                               |                                                                                                                    | _    | -43     | -40  | _    |  |

|           | 1.5 MHz < JM -                                    | M – N = the frequency range for which the spurious emission is measured relative to the transmit center frequency. | -    | -45     | -20  | dBm  |  |

| BLE       | N  < 2.5 MHz<br> M − N <br>≥ 2.5 MHz <sup>b</sup> |                                                                                                                    | -    | -50     | -30  | dBm  |  |

|           | 3.5 MHz <  M –<br>N  < 4.5 MHz                    | M – N = the frequency range for                                                                                    | _    | -50     | -20  | dBm  |  |

| BLE2      | 4.5 MHz (IM – which the sourious emission is      | _                                                                                                                  | -50  | -20     | dBm  |      |  |

|           |                                                   | _                                                                                                                  | -55  | -30     | dBm  |      |  |

Table 16. Bluetooth 2.4 GHz transmitter RF specification (derived from simulation) (continued)

| Parameter                                | Conditions            |                                                                                 | Min. | Typical          | Max. | Unit        |

|------------------------------------------|-----------------------|---------------------------------------------------------------------------------|------|------------------|------|-------------|

| Out-of-Band Emissions <sup>a</sup>       |                       |                                                                                 |      |                  |      |             |

|                                          |                       | HD2 with TX at full power                                                       | _    | -15              | _    | dBm/<br>MHz |

|                                          | Normal-<br>Power mode | HD3 with TX at full power                                                       | _    | -18              | _    | dBm/<br>MHz |

| TX harmonics (HD2, HD3, HD4)             |                       | HD4 with TX at full power                                                       | _    | -30              | _    | dBm/<br>MHz |

| Chip Pout = 14 dBm, BDR<br>and BLE modes |                       | HD2 with TX at full power                                                       | _    | -9               | _    | dBm/<br>MHz |

|                                          | Beamforming<br>mode   | HD3 with TX at full power                                                       | _    | -14              | _    | dBm/<br>MHz |

|                                          |                       | HD4 with TX at full power                                                       | _    | -25              | _    | dBm/<br>MHz |

|                                          | ut = 14 dBm, BDR      | VCO spur at<br>fundamental<br>frequency<br>over the full<br>TX dynamic<br>range | _    | -50              | -    | dBm/<br>MHz |

|                                          |                       | 30 MHz to 1<br>GHz                                                              | _    | -47              | _    | dBm/<br>MHz |

|                                          |                       | 1 GHz to 12.75<br>GHz                                                           | _    | -35              | _    | dBm/<br>MHz |

|                                          |                       | 1.8 GHz to 1.9<br>GHz                                                           | _    | N/A <sup>c</sup> | _    | dBm/<br>MHz |

| TX spurs                                 |                       | 5.15 GHz to<br>5.3 GHz                                                          | _    | N/A <sup>c</sup> | _    | dBm/<br>MHz |

| Chip Pout = 14 dBm, BDR<br>and BLE modes |                       | VCO spur at<br>fundamental<br>frequency<br>over the full<br>TX dynamic<br>range | _    | -45              | _    | dBm/<br>MHz |

|                                          | Beamforming mode      | 30 MHz to 1<br>GHz                                                              | _    | -43              | _    | dBm/<br>MHz |

|                                          |                       | 1 GHz to 12.75<br>GHz                                                           | _    | -29              | _    | dBm/<br>MHz |

|                                          |                       | 1.8 GHz to 1.9<br>GHz                                                           | _    | N/A              | _    | dBm/<br>MHz |

|                                          |                       | 5.15 GHz to<br>5.3 GHz                                                          | _    | N/A              | _    | dBm/<br>MHz |

Table 16. Bluetooth 2.4 GHz transmitter RF specification (derived from simulation) (continued)

| Parameter   | Cond                  | ditions                                    | Min. | Typical | Max. | Unit   |

|-------------|-----------------------|--------------------------------------------|------|---------|------|--------|

| Noise floor |                       | 600-960<br>MHz                             | _    | -163    | _    | dBm/Hz |

|             |                       | 1170-1184 MHz<br>(GPS L5)                  | _    | -158    | _    | dBm/Hz |

|             |                       | 1570-1610<br>MHz (GPS +<br>GLONASS)        | _    | -153    | _    | dBm/Hz |

|             |                       | 1440-1520<br>MHz (B11, B21,<br>B32)        | _    | -154    | _    | dBm/Hz |

|             |                       | 1805-1880<br>MHz (GSM +<br>WCDMA)          | _    | -148    | _    | dBm/Hz |

|             |                       | 1900-1920<br>MHz (GSM +<br>WCDMA)          | _    | -148    | _    | dBm/Hz |

|             |                       | 1930-1990<br>MHz (GSM +<br>WCDMA)          | _    | -147    | _    | dBm/Hz |

|             |                       | 2010-2025<br>MHz<br>(TDSCDMA)              | _    | -146    | _    | dBm/Hz |

|             | Normal-<br>Power mode | 2110-2170<br>MHz<br>(WCDMA)                | _    | -143    | _    | dBm/Hz |

|             |                       | 2300-2370<br>MHz (B40<br>TDD)              | _    | -128    | _    | dBm/Hz |

|             |                       | 2510-2690<br>MHz                           | _    | -128    | _    | dBm/Hz |

|             |                       | 3400-3800<br>MHz (B42,<br>B43)             | _    | -148    | _    | dBm/Hz |

|             |                       | 3800-4200<br>MHz (5G NR<br>n77)            | _    | -148    | _    | dBm/Hz |

|             |                       | 4400-5000<br>MHz (5G NR<br>n79)            | _    | -148    | _    | dBm/Hz |

|             |                       | 5150-5925<br>MHz                           | _    | -156    | _    | dBm/Hz |

|             |                       | 5925-6525<br>MHz<br>(UNII-5-6,<br>UWB CH5) | -    | -160    | -    | dBm/Hz |

|             |                       | 7737-8237<br>MHz (UWB<br>CH9)              | _    | -160    | _    | dBm/Hz |

- a. Applicable to BT normal-power mode TX.

- b. The typical number is measured at ±3 MHz offset.

- c. No visible spurs above the noise floor.

### 6.4. Bluetooth Local Oscillator Performance

Table 17. Local oscillator performance

| Parameter                                 | Minimum     | Typical | Maximum | Unit      |  |  |  |

|-------------------------------------------|-------------|---------|---------|-----------|--|--|--|

| LO Performance                            |             |         |         |           |  |  |  |

| Lock time                                 | _           | 72      | _       | μs        |  |  |  |

| Initial carrier frequency tolerance       | _           | ±25     | ±75     | kHz       |  |  |  |

| Freq                                      | uency Drift |         |         |           |  |  |  |

| DH1 packet                                | _           | ±8      | ±25     | kHz       |  |  |  |

| DH3 packet                                | _           | ±8      | ±40     | kHz       |  |  |  |

| DH5 packet                                | _           | ±8      | ±40     | kHz       |  |  |  |

| Drift rate                                | _           | 5       | 20      | kHz/50 μs |  |  |  |

| Frequency Deviation                       |             |         |         |           |  |  |  |

| 00001111 sequence in payload <sup>a</sup> | 140         | 155     | 175     | kHz       |  |  |  |

| 10101010 sequence in payload <sup>b</sup> | 115         | 140     | _       | kHz       |  |  |  |

| Channel spacing                           | _           | 1       | _       | MHz       |  |  |  |

a. This pattern represents an average deviation in payload.

### 6.5.IEEE 802.15.4 Receiver and Transmitter RF Performance

Table 18. IEEE 802.15.4 receiver and transmitter RF specification

| Parameter                                   | Conditions              | Min. | Typic<br>al | Max.       | Unit |  |  |

|---------------------------------------------|-------------------------|------|-------------|------------|------|--|--|

| Frequency range                             | _                       | 2402 | _           | 2480       | MHz  |  |  |

| Receiver Specification                      |                         |      |             |            |      |  |  |

| Receive sensitivity with dirty transmit off | 250 kbps, OQPSK, 1% PER | _    | -106        | -<br>103.5 | dBm  |  |  |

| Adjacent channel interference               | 1% PER                  | 0    | _           | _          | dB   |  |  |

| Alternate adjacent channel interference     | 1% PER                  | 30   | _           | _          | dB   |  |  |

| Transmitter Specification                   |                         |      |             |            |      |  |  |

b. Pattern represents the maximum deviation in payload for 99.9% of all frequency deviations.

Table 18. IEEE 802.15.4 receiver and transmitter RF specification (continued)

| Parameter                                                                        | Conditions                                                         | Min. | Typic<br>al | Max. | Unit |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------|------|-------------|------|------|

| TX output power at the chip output that meets the IEEE 802.15.4 EVM requirement. | OQPSK. 2:1 VSWR for all phase angles over voltage and temperature. | 13   | _           | ı    | dBm  |

| TV output spoetrum mask                                                          | f - f <sub>c</sub>   > 3.5 MHz (relative)                          | _    | _           | -25  | dBc  |

| TX output spectrum mask                                                          |                                                                    | _    | _           | -35  | dBm  |

# 7. Power Consumption

Note: Values in this data sheet are design goals and are subject to change based on the results of device characterization. Unless otherwise stated, these values apply for the conditions specified in Table 3. The BLE power consumption measurements are shown in Table 19.

Table 19. Bluetooth and BLE power consumption<sup>a</sup>

|                                                     | Operating Mode                      | VDDrail = 3.3V<br>(mW) | VDDrail = 1.05V<br>(mW) | VDDrail = 1.8V<br>(mW) |  |  |  |  |  |

|-----------------------------------------------------|-------------------------------------|------------------------|-------------------------|------------------------|--|--|--|--|--|

| ldle mode                                           |                                     | TBD                    | TBD                     | TBD                    |  |  |  |  |  |

|                                                     | Receive Modes                       |                        |                         |                        |  |  |  |  |  |

| Normal mode                                         | BDR                                 | 2.48                   | 27.72                   | 0.30                   |  |  |  |  |  |

| Normal mode                                         | EDR                                 | 2.48                   | 28.04                   | 0.30                   |  |  |  |  |  |

| Normal mode                                         | BLE                                 | 2.72                   | 26.88                   | 0.30                   |  |  |  |  |  |

| Concurrent mode<br>maximal ratio<br>combining (MRC) | BDR                                 | 2.64                   | 35.91                   | 0.32                   |  |  |  |  |  |

| Concurrent mode maximal ratio combining (MRC)       | EDR                                 | 2.67                   | 36.44                   | 0.32                   |  |  |  |  |  |

| Concurrent mode<br>maximal ratio<br>combining (MRC) | BLE                                 | 2.63                   | 33.92                   | 0.32                   |  |  |  |  |  |

|                                                     | Trans                               | mit Modes              |                         |                        |  |  |  |  |  |